以前設計した回路には、重大な盲点がありました。 2点あります。

- 割り込み要求線に^RD/^WRを入れておかないと、おかしなタイミングで割り込み要求がかかる

- Z80からのI/O要求に対する応答が間に合わない

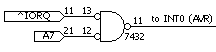

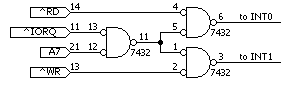

割り込み要求線

I/O要求のタイミング以前の設計では、割り込み要求は次のようにしていました。

IORQの確定とRD/WRの確定には時間差があるようで、どうもIORQの確定のほうが早いようです。 そのため、割り込み要求後にRD/WR線を調べないと本当にI/Oアクセスがかかっているのか分からないです。

そのため、INT線に入れる要求はRDまたはWRとORを取っておく必要があります。

なお、デコードに常にA7を入れているのは、PC-6001の場合、I/Oポート0x80~はシステムによって予約されているためです。

以前設計していたときは、Z80(約4MHz)のin/out命令のスピードが最低でも13クロックかかるため、8MHzのAVRなら26命令分の余裕があると思っていました。

ところが、これが大間違いだったのです。 I/Oの実際の信号が出るのは、命令読み込みではなく命令実行のタイミングのため、IORQが確定するのはかなり遅くなります。

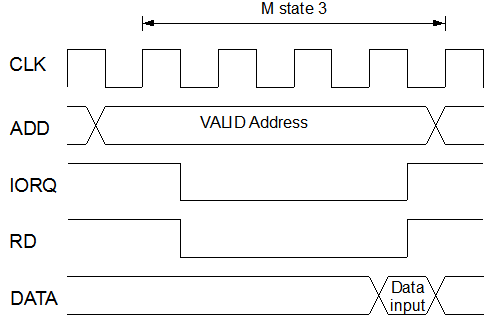

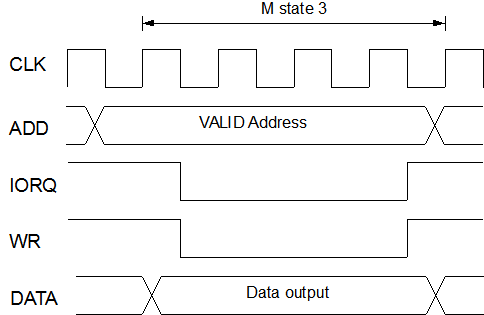

もっとも高速なIN A, (n)やOUT (n), Aで考えても、M1ステートで命令を読み込み、M2ステートでI/Oアドレスを読み込むので、実際のI/O処理が行われるのはM3ステートのみです。

データシートを元に考えると、おおよそ以下の図のようになります。

IN A, (n)のM3ステート時の動作

OUT (n), AのM3ステート時の動作

すると、I/Oリクエストによる割り込みからデータ入出力まではZ80クロック基準で2.5クロック分くらいしか余裕がないのです。

これに対処するには、8MHzのAVRの割り込み処理ではとても追いつきません。 専用のデコーダと入出力用のデータバッファが必要になります。

ていうか、一般的にはこれは常識っぽいですよね。 8255がある理由がそうですから。 なんと間抜けなことをしたことか...。

匿名

画面が真っ暗、でもカーソルは出てる状況。

探して、ここにたどり着きました。

パスワード入力で、復活!

修理に出す寸前でした。ホントにありがとう!