PC-6001で垂直同期が取れるのか。

それを調べるため、DMA ON/OFFを繰り返したときにどうなるのか、試してみました。 プログラムは以下のようなものを使いました。 WAITの影響を少なくするため、RAMで動作させます。

di loop: ld a, #0x02 out (#0x93), a call wait ld a, #0x03 out (#0x93), a call wait jp loop ;; T-state: 2840(incl. call) wait: ld hl, #100 wait_loop: dec hl ld a, h or l jp nz, wait_loop ret

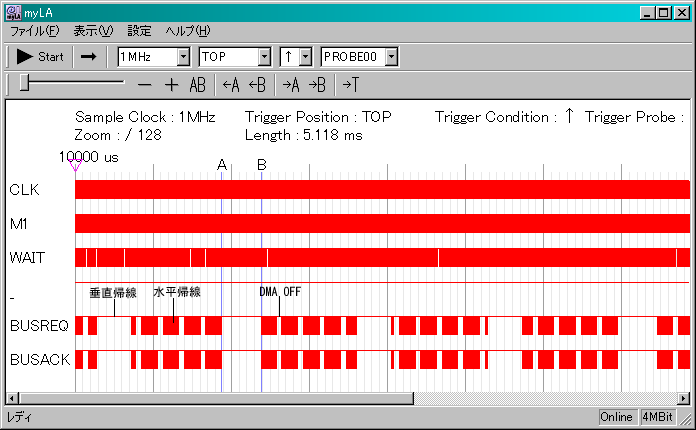

実行の全体像は以下の図のようになります。

記録時間を長くするため、記録周期を粗くしている(1MHz)ので、CLKやM1、WAITは信号ドロップにより不正確です。

気にしないでください。

BUSREQ/BUSACKのみ見てください。

この図で、A-B区間は垂直帰線と推測されます。

赤くなっている部分は、H/Lが細かい周期で繰り返されている箇所です。

水平帰線によりH/Lを繰り返しているのでしょう。

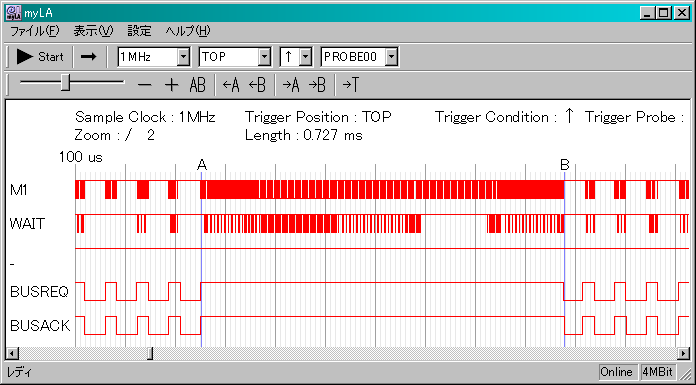

これは、赤い部分に挟まれた短いHの期間をズームしたものです。 ここはDMA OFFでwaitを実行している部分でしょう。 A-Bの時間(727us)は、DMA OFF時のの論理実行時間(約720us)にきわめて近くなっており、予測は正しそうです。

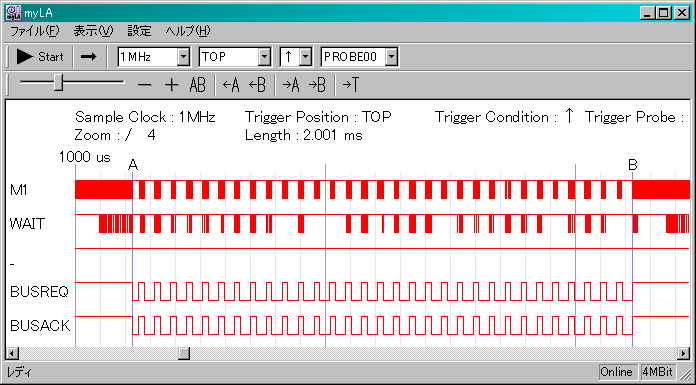

さらに、赤い部分(H/Lが密で、水平帰線を繰り返している部分)のズームです。 本当なら水平線の本数は192本あり、その分のLを繰り返すはずが、ここでは32本分しかありません。 Bの部分でDMA OFFにしているためです。

少なくともここで言えるのは、「ポート0x93のコントロールによるVDGのDMAのON/OFFは垂直帰線に同期しているわけではない」ということです。

残念ながら。

さらに調べると、この計測における一つの水平帰線(BUSACK=L)の時間は40~41usなのですが、DMA ON直後のBUSACK=Lの時間(上図でAから始まるBUSACK=L部分)はそれより短い(21~25usくらい)という結果でした。逆に、DMA OFF直前のBUSACK=Lの時間(上図Bで終わる部分)は41usになっています。垂直帰線によるBUSACK=Hが終わった直後のBUSACK=L(最初の図のBの直後)もおよそ41usです。すなわち、DMA OFFからONにした直後のみDMAが占有する時間が少ないことになります。

これが何を意味するのかはまだよくわかりません。

もう少し考察が必要ですね。また、何か別の方法も考えねば...。

匿名

画面が真っ暗、でもカーソルは出てる状況。

探して、ここにたどり着きました。

パスワード入力で、復活!

修理に出す寸前でした。ホントにありがとう!